# 캐시 교체 정책에 따른 성능 및 면적 비교 연구

조상원<sup>1</sup>, 박현진<sup>1</sup>

<sup>1</sup> 성균관대학교 전자전기공학부

[Swjo1999@skku.edu](mailto:Swjo1999@skku.edu), hyunjinp@skku.edu

## A Study on Performance and Area Comparison according to cache replacement policy

Sang-Won Jo<sup>1</sup>, Hyunjin Park<sup>1</sup>

Dept. of Electrical Engineering, Sung-Kyun-Kwan University

### 약

캐시는 현대 컴퓨터 시스템에서 중요한 성능 개선 요소 중 하나로, 효율적인 데이터 저장 및 액세스를 보장한다. 교체 정책은 캐시의 한정된 용량 내에서 어떤 데이터를 보관하고 어떤 데이터를 대체할지 결정하는 데 중요한 역할을 한다. 이 논문은 Pseudo LRU와 LRU 교체 정책을 대상으로 cache에서의 throughput과 gate count를 각각 비교한다. LRU 방식을 적용한 cache와 Pseudo LRU 방식을 적용한 cache는 Locality 0과 100에서 0.001GB/s 미만의 차이를 보이며 각각 0.095GB/s, 0.211GB/s로 동일했으며 Gate Count는 각각 134,516과 130,016으로 4500의 감소 효과가 있었다.

### 1. 서론

현대 컴퓨팅 시스템은 점차적으로 복잡성을 높이며 성능 향상을 위해 다양한 기술적 개선을 도입하고 있다. 이러한 개선은 대용량 데이터 처리에 있어서 캐시 메모리의 중요성을 더욱 부각시켰다. 캐시는 빠른 데이터 액세스를 통해 프로세서와 메인 메모리 간의 병목 현상을 완화하고, 프로그램 실행 속도를 향상시키는 역할을 수행한다.[1]

캐시의 효율적인 관리는 성능 향상을 위해 결정적인 역할을 한다. 데이터 액세스 패턴은 대부분의 경우 지역성을 가지기 때문에, 최근에 사용되지 않은 데이터는 미래에도 사용되지 않을 가능성이 높다. 따라서, 캐시 메모리 용량을 한정적으로 사용하면서도 주로 사용되는 데이터를 저장하기 위해서는 캐시 교체 정책이 필요하다.[2]

캐시 교체 정책 중 하나인 LRU(Least Recently Used) 정책은 가장 오래 전에 사용된 데이터를 대체하는 방식으로 동작하며, 이론적으로 최적의 교체 정책이지만 실제 구현에서는 메모리 접근 패턴을 추적하는 데 필요한 비트를 유지하는 복잡성과 비용의 문제가 있다. 또 다른 캐시 교체 정책인 Pseudo LRU는 이러한 복잡성을 줄이면서도 LRU에 근사한 성능을 제공하려는 시도로 개발되었다. 이 논문에서는 4way set associative cache에서의 Pseudo LRU와 LRU 교체 정책에 초점을 맞추어 그 효과를 비교 분석한다.

### 2. 본론

#### 1) LRU

| LRU : Way0 |         | Row -> 0 | Column -> 1 |

|------------|---------|----------|-------------|

| Way0       | 1 1 1 1 | 0 0 0 0  | 1 0 0 0     |

| Way1       | 0 1 1 1 | 0 1 1 1  | 1 1 1 1     |

| Way2       | 0 0 1 1 | 0 0 1 1  | 1 0 1 1     |

| Way3       | 0 0 0 1 | 0 0 0 1  | 1 0 0 1     |

1. Initial value

| Row -> 0 |         | Column -> 1 |

|----------|---------|-------------|

| Way0     | 1 0 0 0 | 1 1 0 0     |

| Way1     | 0 0 0 0 | 0 1 0 0     |

| Way2     | 1 0 1 1 | 1 1 1 1     |

| Way3     | 1 0 0 1 | 1 1 0 1     |

2. Cache Miss

| Row -> 0 |         | Column -> 1 |

|----------|---------|-------------|

| Way0     | 0 0 0 0 | 1 0 0 0     |

| Way1     | 0 0 0 0 | 0 1 0 0     |

| Way2     | 1 0 1 1 | 1 1 1 1     |

| Way3     | 1 0 0 1 | 1 1 0 1     |

3. LRU : Way1

| Row -> 0 |         | Column -> 1 |

|----------|---------|-------------|

| Way0     | 0 0 0 0 | 1 1 0 0     |

| Way1     | 0 0 0 0 | 0 1 0 0     |

| Way2     | 1 0 1 1 | 1 1 1 1     |

| Way3     | 1 0 0 1 | 1 1 0 1     |

4. Cache Miss

| Row -> 0 |         | Column -> 1 |

|----------|---------|-------------|

| Way0     | 0 0 0 0 | 1 0 0 0     |

| Way1     | 0 0 0 0 | 0 1 0 0     |

| Way2     | 1 1 1 1 | 1 1 1 1     |

| Way3     | 1 1 0 1 | 1 1 0 1     |

5. Cache Miss

| Row -> 0 |         | Column -> 1 |

|----------|---------|-------------|

| Way0     | 0 0 0 0 | 1 0 0 0     |

| Way1     | 0 0 0 0 | 0 1 0 0     |

| Way2     | 1 1 1 1 | 1 1 1 1     |

| Way3     | 1 1 0 1 | 1 1 0 1     |

6. LRU : Way2

| Row -> 0 |         | Column -> 1 |

|----------|---------|-------------|

| Way0     | 0 0 0 0 | 1 0 0 0     |

| Way1     | 0 0 0 0 | 0 1 0 0     |

| Way2     | 1 1 1 1 | 1 1 1 1     |

| Way3     | 1 1 0 1 | 1 1 0 1     |

7. Cache Hit (Way0)

| Row -> 0 |         | Column -> 1 |

|----------|---------|-------------|

| Way0     | 0 0 0 0 | 1 0 0 0     |

| Way1     | 0 0 0 0 | 0 1 0 0     |

| Way2     | 1 1 1 1 | 1 1 1 1     |

| Way3     | 1 1 0 1 | 1 1 0 1     |

8. Cache Hit

| Row -> 0 |         | Column -> 1 |

|----------|---------|-------------|

| Way0     | 0 0 0 0 | 1 0 0 0     |

| Way1     | 0 0 0 0 | 0 1 0 0     |

| Way2     | 1 1 1 1 | 1 1 1 1     |

| Way3     | 1 1 0 1 | 1 1 0 1     |

6. LRU : Way2

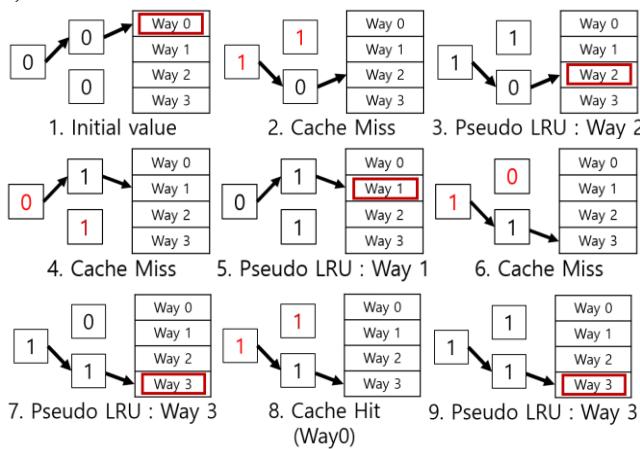

## 2) Pseudo LRU

## 3) LRU, Pseudo LRU Throughput, Gate Count 비교

4way set associative cache 에 LRU, Pseudo LRU 를 각각 적용하고 Throughput 과 Gate Count 를 측정했다. Throughput 은 Locality 0, 50, 100 의 상황에서 비교를 진행했다.

<표 1> LRU, Pseudo LRU 각각을 적용한 4way set associative cache 비교

|                          | LRU cache    | Pseudo LRU cache |

|--------------------------|--------------|------------------|

| Throughput (Locality0)   | 0.095 (GB/s) | 0.095 (GB/s)     |

| Throughput (Locality50)  | 0.127 (GB/s) | 0.126 (GB/s)     |

| Throughput (Locality100) | 0.211 (GB/s) | 0.211 (GB/s)     |

| Gate Count               | 134,516      | 130,016          |

<표 1>을 통해 알 수 있듯이 LRU 정책을 적용한 cache 에서의 성능이 Pseudo LRU cache 의 성능보다 높다. LRU 와 Pseudo LRU 의 Throughput 차이는 1% 미만이다. LRU 를 적용한 cache 의 Gate Count 보다 Pseudo LRU 를 적용한 cache 가 4% 미만의 Gate Count 감소가 있었다. 1% 미만의 성능 감소를 통해 3% 이상의 Gate Count 감소 효과를 볼 수 있다.

## 3. 결론

본 연구는 4-way set associative cache 에 LRU 와 Pseudo LRU 교체 정책을 각각 적용하여 Throughput 과 Gate Count 를 평가하였다. 실험은 Locality 0, 50, 100 의 상황에서 진행되었으며, <표 1>을 통해 얻은 결과를 분석하였다.

실험 결과에 따르면, LRU 정책을 적용한 캐시가 Pseudo LRU 캐시보다 더 우수한 성능을 나타내었다. 두 교체 정책의 Throughput 차이는 1% 미만으로 나타났으며, Pseudo LRU 를 적용한 캐시는 LRU 를 적용한 캐시에 비해 4% 미만의 Gate Count 감소를 보였다. 이러한 결과는 1% 미만의 성능 저하에 대비하여 3% 이상의 Gate Count 감소 효과를 얻을 수 있다는 것을 시사한다.

종합하면, LRU 와 Pseudo LRU 교체 정책을 4-way set associative cache 에 적용한 결과, LRU 정책이 더 나은 성능을 제공하며 Pseudo LRU 를 적용한 캐시는 gate count 측면에서도 이점을 갖는다는 결론을 얻을 수 있었다. 이러한 연구 결과는 캐시 교체 정책의 선택이 성능 및 자원 사용 측면에서 중요하며, 특히 실제 운용 환경과 응용 프로파일을 고려하여 최적의 결정을 하는 것이 필요함을 강조한다.

## ACKNOWLEDGMENT

이 논문은 정부(교육부-산업통상자원부)의 지원으로 한국산업기술진흥원의 지원을 받아 수행된 연구임 (P0022098, 2023 년 미래형자동차 기술융합 혁신인재양성사업)

- [1] Steven A. Przybylski "Cache and Memory Hierarchy Design" 1rd Ed. Elsevier Science, 1990.

- [2] Akanksha Jain "Cache Replacement Policies" 1rd Ed. Springer International Publishing, 2022.