# FPGA기반 저지연 데이터 이벤트 탐지 모듈 구현 윤기하, 김재인, 김성창 한국전자통신연구원

{gya, jaein, sungchang}@etri.re.kr

# A Study on the FPGA based low-latency data event detector implementation

Yoon Giha, Kim Iaein, Kim Sung Chang Electronics and Telecommunications Research Institute

요 약

이 논문에서는 저지연 IoT/IIoT 응용 서비스를 위하여 실시간으로 취득되는 센서 데이터로부터 사용자가 정의한 이벤트에 해당하는 데이터를 최소 지연으로 탐지할 수 있는 FPGA 기반의 하드웨어 모듈 구현에 대한 연구내용을 기술한다. Intel SoC FPGA 기반 개발보드를 활용하여 이벤트 탐지 모듈을 구현하였으며, RS485 통신기반으로 동작하는 전력품질 측정 센서를 활용한 실험환경에서 이벤트를 탐지 및 CPU로의 전송 시간은 평균 561.75µs 수준으로 확인되었다.

## I. 서 론

IoT(Internet of Things) 및 IIoT(Industrial IoT)에서는 각종 장치나 센서로부터 데이터를 수집하여 이를 가공 처리하는 데이터 수집 장치가 사용된다.[1, 2] 데이터 수집 장치는 단순히 데이터를 수집하여 타 인터페이 스로 전달하는 일종의 게이트웨이 이며, 최근 수집한 데이터를 처리, 분석, 저장할 수 있는 엣지 컴퓨팅 기술이 게이트웨이에 적용되고 있다. 엣지 컴 퓨팅기반의 게이트웨이는 각각의 응용서비스에 따라 범용적으로 적용될 수 있도록 다양한 수집용 인터페이스 및 복수의 프로토콜을 탑재한 프로 세서 시스템으로 구성된다.[3] 이 논문에서는 프로세서 시스템이 탑재된 SoC FPGA를 활용하여 RS485기반의 전력센서로부터 획득되는 다양한 전력품질데이터의 사용자 정의 이벤트를 최소지연으로 획득하는 저지연 이 벤트 탐지 모듈 설계 및 구현에 대하여 기술한다.

#### Ⅱ. FPGA기반 저지연 이벤트 탐지 모듈 구현

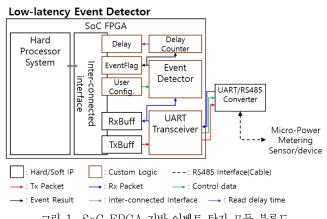

이 연구에서 제안하는 저지연 이벤트 탐지 기능은 데이터 획득 대상 (센서)으로부터 데이터가 수신되어 수신버퍼에 쌓기 전 단계(Media Access Control Layer)에서 사용자가 정의한 이벤트 발생 여부를 판별하여 프로세서에 결과를 알릴 수 있도록 설계하였다. 하드웨어로 구현된 이벤트 탐지 모듈을 활용하면 프로세서로 처리하는 이벤트 판별에 관한 일련의 과정을 생략할 수 있어, OS(Operating System)기반 환경에서 복수 프로 그램 동작에 의한 부하로부터 생길 수 있는 센서 데이터 취득 시점의 비주기성을 억제할 수 있다. 이 연구에서는 INTEL사의 SoC FPGA(System on a Chip with Field-Programmable Gate Array)인 Cyclone V SE 시리즈 (5CSEBA6U23I7)를 탑재한 TERASIC사 개발보드(DE10-Nano Kit)를 활용하였다. 이 연구에 사용된 개발보드는 800MHz로 동작하는 Dual-core ARM Cortex-A9 프로세서 및 1GB DDR3 메모리를 포함한 컴퓨팅 시스템이 FPGA 내에 Hard IP(Intellectual Property) 형태로 집적되어, 프로세서와 FPGA간 내부 인터페이스를 통해 고속으로 데이터를 전달할 수 있다.[4] 아래 그림 1은 이 연구를 통해 설계한 SoC FPGA 기반 이벤트 탐지 모듈의

기능블록도를 나타낸다. 그림 1과 같이 FPGA 영역에서 하드웨어로 설계한 이벤트 탐지 기능블록은 UART(Universal Asynchronous Receiver/Transmitter) 송·수신 기능블록과 수신버퍼(RxBuff) 사이에서 1바이트 단위로 수신 프레임을 수집하여 실시간으로 이벤트를 탐지할 수 있도록 설계하였다. 사용자는 User Config. 기능블록을 통해 탐지대상 데이터의 위치, 크기, 탐지 조건 및 비교 데이터 정의할 수 있다.

그림 1. SoC FPGA 기반 이벤트 탐지 모듈 블록도

수신 데이터를 실시간으로 감시하여 사용자 정의 이벤트 여부를 탐지한 결과는 SoC FPGA 내부 인터페이스를 통해 프로세서에서 읽을 수 있도록 설계하였다. 이벤트 탐지에 대한 결과를 EventFlag 레지스터에 갱신하며, 갱신과 함께 Delay Counter를 구동하여 프로세서가 이벤트 탐지 결과를 읽는데 소요되는 지연시간을 확인할 수 있도록 부가 기능블록을 추가하였다. 이벤트 탐지 결과 획득 지연시간은 Delay Counter를 통해 FPGA 영역에서 생성·계산되며, 이 기능을 바탕으로 구현한 저지연 이벤트 탐지 모듈의 이벤트 탐지 지연시간을 확인하였다. 이 연구에서 사용한 개발보드의 프로세서 시스템에는 리눅스 Ubuntu16.04 LTS(Long-Term Support)를 탑재하였다. 따라서, 프로세서가 내부 인터페이스를 통한 FPGA와 데이터 전달·획득에 소요되는 시간에 불규칙한 편차가 존재한다.[5] 프로세서에서

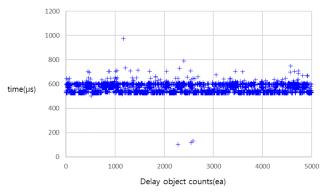

Delay 값을 읽은 뒤, 읽음 신호를 다시 한번 FPGA에 전달하는 절차까지 이벤트 탐지 지연시간으로 정의하였다. 이와 같은 환경에서 개발한 저지연 이벤트 탐지 모듈의 이벤트 탐지 지연시간은 최소 101.49µs에서 최대 972.26µs로 확인되었으며 평균 561.75µs 성능을 보이는 것으로 확인하였다. 그림 2는 본 연구에서 구현한 저지연 이벤트 탐지 모듈의 이벤트 탐지 지연시간을 데이터 획득시간 순으로 나열한 것이다.

그림 2. 제안 모듈의 이벤트 탐지 지연시간 측정 결과(5,000개 샘플)

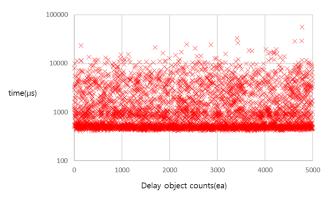

위 그림 2에서 보이는 바와 같이 FPGA 기반의 하드웨어 지원을 통한 이벤트 탐지 지연시간의 최대 편차가 870.77µs로 확인되었다. 아래 그림 3은 SoC FPGA 내에 집적된 Dual-core ARM Cortex-A9 프로세서에 의존한 소프트웨어 기반 이벤트 탐지 지연시간 결과 샘플을 나열한 것이다.

그림 3. S/W 기반 이벤트 탐지 지연시간 측정 결과(5,000개 샘플)

집적된 프로세서 기반의 소프트웨어 이벤트 탐지 지연시간은 최소 407.51us에서 최대 55.82ms으로 평균 1.70ms 수준으로 확인되었다.

위 그림 2, 3에서 보이는 것과 같이 제안한 FPGA기반 저지연 이벤트 탐지 모듈이 소프트웨어 처리기반의 이벤트 탐지 지연시간 편차 55.41ms 대비 약 1.57% 수준의 적은 편차로 동작하는 것을 확인할 수 있다. 아래 표 1은 제안한 저지연 이벤트 탐지 모듈과 소프트웨어 기반 이벤트 탐지 성능 비교표이다.

표 1. 소프트웨어 기반 이벤트 탐지 및 저지연 이벤트 탐지 모듈 성능 비교

| Delay Type | *Event Detector | Software |

|------------|-----------------|----------|

| Min.       | 101.49          | 407.51   |

| Max.       | 972.26          | 55817.56 |

| Deviation  | 870.77          | 55410.05 |

| Avg.       | 561.75          | 1697.37  |

(Unit:µs)

표 1에서 보이는 것처럼 제안한 FPGA 기반의 저지연 이벤트 탐지 모듈은 소프트웨어 기반의 이벤트 탐지보다 약 4배에서 549.9배 우수한 성능을 갖는 것으로 확인되었다.

#### Ⅲ. 결 론

본 논문에서는 IoT/IIoT 분야에서 센서로부터 데이터를 수집함에 있어, 사용자 정의에 따른 이벤트를 최소지연으로 탐지하기 위한 SoC FPGA 기반의 저지연 이벤트 탐지 모듈 설계 및 구현에 대하여 기술하였다. 프로세서가 집적된 SoC FPGA는 제안한 이벤트 탐지 모듈을 프로세서에서 고속으로 접근하기 용이한 구조로 FPGA 영역에 구현된 하드웨어 기능으로부터 이벤트 탐지 결과를 획득하는데 평균 561.75µs 소요됨을 확인하였다. 이러한 기술은 복수의 센서로부터 데이터를 취득하며 이벤트를 탐지하는 응용의 하드웨어 지원부분, 인공지능 학습결과를 바탕으로 작성된 Look-Up Table 기반의 학습형 이벤트 탐지 등 IoT/IIoT 분야에서 특수목적 이벤트를 빠르게 탐지하여 대처하기 위한 기반 기술로 활용할 수 있다.[6, 7]

#### ACKNOWLEDGMENT

본 연구 논문은 한국전자통신연구원 연구운영지원사업의 일환으로 수행되었음.[20ZK1100, 호남권 지역산업 기반 ICT 융합기술 고도화 지원사업]

### 참고문헌

- [1] L. D. Xu, W. He and S. Li, "Internet of Things in Industries: A Survey," Nov. 2014. IEEE Transactions on Industrial Informatics, Vol. 10, no. 4, pp. 2233–2243.

- [2] Young Seog Yoon, Hangjung Zo, Munkee Choi, Donghyun Lee, and Hyun-woo Lee. "Exploring the dynamic knowledge structure of studies on the Internet of things: Keyword analysis," Nov. 2018. ETRI Journal Vol. 40(6), pp. 745–758.

- [3] Dell, "IoT Deployment Is Driving Analytics To The Edge", April. 2019. (https://www.delltechnologies.com/en-us/)

- [4] terasIC, "DE10-Nano User Manual (rev. A/B Hardware) version 1.8", Feb. 2018. (https://www.terasic.com.tw)

- [5] Intel, "Cyclone V Hard Processor System Technical Reference Manual," Sep. 2020. (https://www.intel.com)

- [6] Giha Yoon, Jaein Kim, Geun-Yong Kim, Byunghee Son, and Hark Yoo. "Multiple RS-485 interface management FPGA design for Power micro-metering," ICPE 2019-ECCE Asia, pp. 2635–2640.

- [7] Sung Il Na, Hyoung Joong Kim. "Design of Anomaly Detection System Based on Big Data in Internet of Things," Feb. 2018. Journal of Digital Contents Society, Vol. 19(2), pp. 377–383.